Proces návrhu elektronických zařízení se s rostoucí složitostí a nároky neustále mění. Díky novým výrobním procesům lze vytvářet zapojení pracující se stále nižším napájecím napětím a vyššími přenosovými rychlostmi. Od doby, kdy byly standardem logické obvody TTL a 5V CMOS jsme se dostali přes 3,3 V až k 1,8 V, 1,2 V a 0,8 V. Některé z nově navrhovaných integrovaných obvodů dokáží pracovat s ještě o něco nižším napájecím napětím. To vše také přispívá ke snižování spotřeby elektřiny. Takový trend není pouze výhodným, ale i nutným. Miliardy vyrobených elektronických zařízení ročně, musí být napájeny až neuvěřitelným množstvím energie.

Proces návrhu elektronických zařízení se s rostoucí složitostí a nároky neustále mění. Díky novým výrobním procesům lze vytvářet zapojení pracující se stále nižším napájecím napětím a vyššími přenosovými rychlostmi. Od doby, kdy byly standardem logické obvody TTL a 5V CMOS jsme se dostali přes 3,3 V až k 1,8 V, 1,2 V a 0,8 V. Některé z nově navrhovaných integrovaných obvodů dokáží pracovat s ještě o něco nižším napájecím napětím. To vše také přispívá ke snižování spotřeby elektřiny. Takový trend není pouze výhodným, ale i nutným. Miliardy vyrobených elektronických zařízení ročně, musí být napájeny až neuvěřitelným množstvím energie.

V tomto článku chci jednoduchým způsobem provést v problematice logických hodnot a jejich napěťových úrovní.

Logické stavy

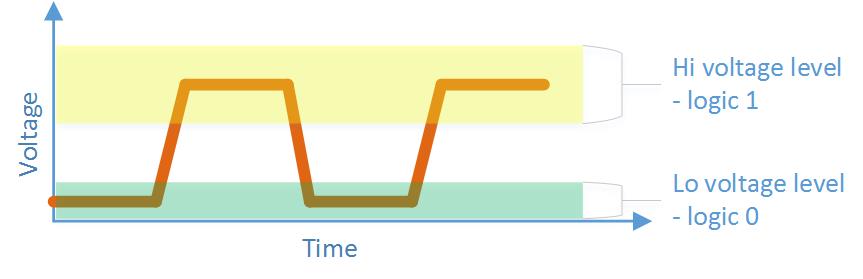

Veškerá současně vyráběná komerční výpočetní technika a elektronika pracuje s tzv. binárními stavy. Ty jsou reprezentovány logickou hodnotou „1“ a logickou hodnotou „0“. Tyto dva základní stavy si lze představit jako rozsvícení žárovky vypínačem. Tedy svítí – 1, nesvítí – 0. Pouhé dvě logické hodnoty tedy řídí celý náš elektronický svět.

Existuje sice ještě obor věnující se kvantovým počítačům a kvantovým stavům, ale ty zde popisovat nebudu, jelikož je to mimo rámec tohoto článku.

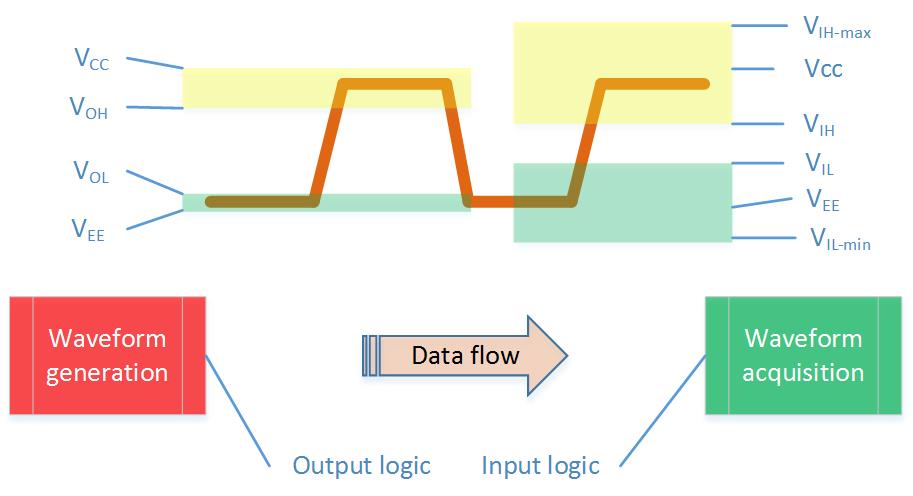

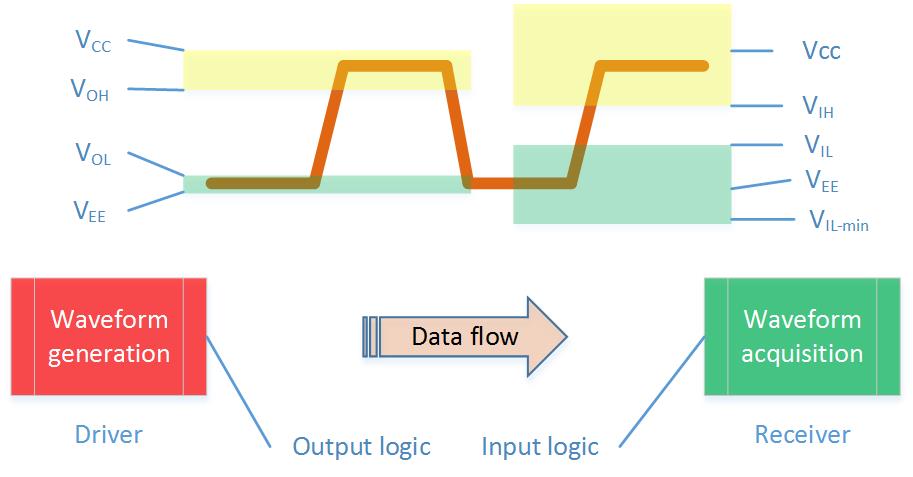

V první řadě je ale nutné rozhodnout, za jakých okolností bude určité napětí reprezentováno jako logická 1 nebo 0. Tomuto milníku se říká rozhodovací úroveň. Bavíme se sice o digitálním signálu, ale ten má určitou formu analogového (změna amplitudy v čase). Aby se předešlo problémům vznikajícím díky fyzikálním zákonům (vliv délky vedený na velikosti přeneseného napětí, vliv kapacity vedení na tvaru signálu), neuvažuje se rozhodovací úroveň pouze jako jedna hodnota napětí, ale interval. Tento interval je také označován jako zakázaná zóna nebo zóna neurčitosti. Tedy oblast, ve které se napětí nesmí objevit. Pokud se tak stane, není zaručeno, jak vstupní obvody přijímající takový signál zareagují. V tomto intervalu tedy dochází k přepnutí stavu z logické 1 na logickou 0 a naopak. V některých technických dokumentech lze konkrétní napěťovou hodnotu tohoto bodu nalézt pod označením VT (Threshold Voltage).

V první řadě je ale nutné rozhodnout, za jakých okolností bude určité napětí reprezentováno jako logická 1 nebo 0. Tomuto milníku se říká rozhodovací úroveň. Bavíme se sice o digitálním signálu, ale ten má určitou formu analogového (změna amplitudy v čase). Aby se předešlo problémům vznikajícím díky fyzikálním zákonům (vliv délky vedený na velikosti přeneseného napětí, vliv kapacity vedení na tvaru signálu), neuvažuje se rozhodovací úroveň pouze jako jedna hodnota napětí, ale interval. Tento interval je také označován jako zakázaná zóna nebo zóna neurčitosti. Tedy oblast, ve které se napětí nesmí objevit. Pokud se tak stane, není zaručeno, jak vstupní obvody přijímající takový signál zareagují. V tomto intervalu tedy dochází k přepnutí stavu z logické 1 na logickou 0 a naopak. V některých technických dokumentech lze konkrétní napěťovou hodnotu tohoto bodu nalézt pod označením VT (Threshold Voltage).

Podíváme-li se na napěťové úrovně podrobněji, zjistíme, že je rozdíl mezi výstupními a vstupními obvody. Tento rozdíl je v toleranci výstupního a vstupního napětí. Tyto rozdíly bylo nutné zavést právě kvůli minimalizaci rizika problémů s přenosem po datových linkách způsobených již zmíněnou délkou vedení, odporem, kapacitou, atp. Výstupní úrovně mají menší toleranci než vstupní. Na obrázku níže je zobrazen digitální signál s příslušnými úrovněmi.

Výstupní logika obvodu generující digitální signál (Waveform generator – Driver) má určen interval napětí logické 1 v rozmezí VOH (Voltage Output High; minimální výstupní napětí pro logickou 1) až VCC (kladné napájecí napětí integrovaného obvodu). Pro logickou 0 je tento interval od napájecí úrovně VEE až po VOL (Voltage Output Low; maximální výstupní napětí pro logickou 0).

Výstupní logika obvodu generující digitální signál (Waveform generator – Driver) má určen interval napětí logické 1 v rozmezí VOH (Voltage Output High; minimální výstupní napětí pro logickou 1) až VCC (kladné napájecí napětí integrovaného obvodu). Pro logickou 0 je tento interval od napájecí úrovně VEE až po VOL (Voltage Output Low; maximální výstupní napětí pro logickou 0).

Vstupní logika obvodu zpracovávajícího digitální signál (Wevaform Acquisition – Receiver) dokáže zpracovávat napětí i mimo své vlastní napájecí. Hodnota VIH (Voltage Input High; minimální vstupní napětí pro logickou 1) má nižší hodnotu nežli VOH. To proto, aby byly kompenzovány ztráty ve vedení, různých technologiích výroby apod. VIH-max (maximální vstupní hodnota napětí pro logickou 1) je nad kladným napájecím napětím VCC. Hodnota VIH-max bývá limitována použitým materiálem při výrobě polovodiče čipu a dalšími vlastnostmi vstupních obvodů. Při překročení tohoto napětí dojde ke zničení vstupních obvodů nebo celého integrovaného obvodu. Příslušná hodnota je u každého integrovaného obvodu jiná. Logická 0 může nabývat napětí od VIL-min (minimální vstupní hodnota napětí pro logickou 0), která se v praxi pohybuje kolem úrovně VEE, ale vstupní obvod dokáže pracovat i se záporným napětím (limity jsou definovány podobně jako v případě VIH-max např. materiálem čipu), až po VIL (Voltage Input Low; maximální vstupní hodnota napětí pro logickou 0). Hodnota VIL je o něco vyšší než VOL. Důvody jsou podobné jako v případě již zmíněného rozdílu parametrů VIH a VOH. U vstupní logiky hovoříme o tzv. napěťové toleranci.

V předchozích odstavcích je užito termínů VCC a VEE. Ty označují kladné (VCC; připojený kolektor tranzistoru – Collector) a GND/záporné (VEE; připojený emitor tranzistoru – Emitter) napájecí napětí v logice TTL, která je založena na bipolárních tranzistorech. V případě logiky CMOS, která je založena na unipolárních tranzistorech řízených polem, se používá označení VDD (kladné napájecí napětí; Drain) a VSS (GND nebo záporné napájecí napětí; Source). Tato označení lze nalézt v datových listech příslušných integrovaných obvodů, případně ve schématech. Nejčastěji se ale můžeme setkat s označením VCC a GND, užívané pro TTL i CMOS.

Stejně jako v případě napěťových úrovní, podobné platí i pro proud. Každým výstupem může při logické 1 nebo logické 0 protékat pouze omezený proud IOH a IOL. Těmto parametrům se říká proudová zatížitelnost výstupu. Současně, každý vstup odebírá při logické 1 i logické 0 určitý proud (proudový odběr) IIH a IIL. Je proto nezbytně nutné s těmito parametry při navrhování obvodů počítat.

Co se ale stane v případě, že na vstup není přivedeno žádné napětí?

V praxi často vstupní logické obvody obsahují tzv. pull-up a pull-down rezistory. Ty nám určují, zda v takovém případě bude tato situace vyhodnocena tak, jako by byla hodnota přivedeného signálu logická 1 (pull-up) nebo logická 0 (pull-down). Pull-up znamená, že je na vstupu zapojen odpor určité hodnoty připojen mezi vstup a kladné napájecí napětí, pull-down naopak značí připojení odporu k logické zemi (nejčastěji 0 V). V závislosti na typu integrovaného obvodu lze tyto odpory nastavovat programově.

Existuje i třístavová a čtyřstavová logika. Ve třístavové logice je přidán stav Z. Jedná se stav vysoké impedance (high-Z), kde je výstup logického obvodu odpojen od okolí – tedy ve stavu vysoké impedance. Tento stav je posléze vyhodnocen a slouží pro informaci, zda má být výstup nějakým způsobem využit (např. automatické přepnutí mezi režimy vstup/výstup; pro připojení dalších funkčních bloků integrovaného obvodu; nebo může být integrovaný obvod spolu s dalšími připojen ke sběrnici, kde může být aktivní pouze jeden – příslušný obvod a jeho výstupy jsou aktivovány signálem EN – enable). Čtvrtý stav X je také doplňkovým a určuje, jak má být nastavena datová linka v průběhu inicializace obvodu nebo zda se má její stav účastnit vyhodnocování v logice integrovaného obvodu. Stavy Z a X nejsou přímo logickými úrovněmi, ale pomáhají při zpracování digitálního signálu.

Aktivní stavy

Logické hodnoty 1 a 0 nemusíme používat pouze pro přenos užitečných dat a stavů, ale můžeme je využít i pro řízení předem definovaných funkcí. V takovém případě bude mít datová linka/pin integrovaného obvodu za úkol na základě určitého stavu provést danou operaci, např. aktivace režimu zápisu u paměťového čipu. Takovému stavu se říká aktivní stav.

Aktivní stav je závislý na vnitřním uspořádání konkrétního čipu a dalších parametrech. Aktivní stav není to samé jako logický stav (1 a 0). Některé obvody lze tedy aktivovat logickou 1, jiné logickou 0. Pro označování aktivních stavů se nicméně také používá binární logika, aktivní 1 (active-high) a aktivní 0 (active-low).

Pokud je vstup označen jako active-high, je pro aktivaci nutné přivést logickou 1. V případě, že je označen jako active-low, aktivuje se přivedením logické 0. Podobný princip lze aplikovat i u výstupu (jedná se zejména o princip značení takového výstupu).

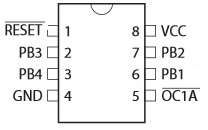

Každá signálová digitální linka, nebo pin integrovaného obvodu, má svůj název. Ten se odvíjí od konkrétní funkce. Kromě vlastního názvu je důležitou informací právě i označení aktivního stavu. Označují se ale pouze aktivní stavy active-low, tedy aktivní při logické 0.

Každá signálová digitální linka, nebo pin integrovaného obvodu, má svůj název. Ten se odvíjí od konkrétní funkce. Kromě vlastního názvu je důležitou informací právě i označení aktivního stavu. Označují se ale pouze aktivní stavy active-low, tedy aktivní při logické 0.

Takto označené vstupy/výstupy nesou znak negace. Například signál EN, aktivní v logické 0, se jmenuje „negovaný EN“, a označuje se EN, *EN, EN_N, EN_B, nEN, EN#, /EN, apod.

Charakteristika digitální linky

Digitální linka je vodič přenášející změny napětí z výstupního obvodu do vstupního. Stejně jako v případě analogového sinusového signálu je potřeba zabezpečit minimální degradaci, zpoždění, ovlivnění jiným signálem a zároveň rušení jiných signálů při přenosu signálu digitálního.

Při návrhu zapojení zařízení a propojení jednotlivých integrovaných obvodů je zapotřebí brát v úvahu řadu parametrů, které se na digitální komunikaci podílejí.

Mezi tyto parametry patří zejména maximální kmitočet přenášeného signálu a rozptyl napěťových úrovní. Na základě těchto a jiných parametrů lze vypočítat nebo odvodit vlnovou délku pro výpočet rozměrů vedení (délka, vzdálenost mezi vodiči), průřezy vodičů, stínění, kapacitu, indukčnost, charakteristickou impedanci, útlum vedení a jiné.

Charakteristiky digitální linky nám předurčují fyzické vlastnosti přenosové soustavy, tzn., zda použijeme koaxiální kabel, kroucenou dvoulinku, dodatečné stínění, speciální konektory, atd. Řada těchto parametrů se uplatňuje zejména při komunikaci vyššími datovými rychlostmi v řádech Mbps – Gbps.

Můžeme říci, že tímto způsobem definujeme fyzickou vrstvu celého systému, která vyhoví našim požadavkům.

Metody přenosu digitálních signálů

Při přenosu digitálních signálů se můžeme setkat se dvěma metodami, které mají různé výhody a nevýhody. A právě k metodám přenosu digitálních signálů se přímo vztahují různé standardizované interpretace napěťových úrovní definující jednotlivé logické hodnoty.

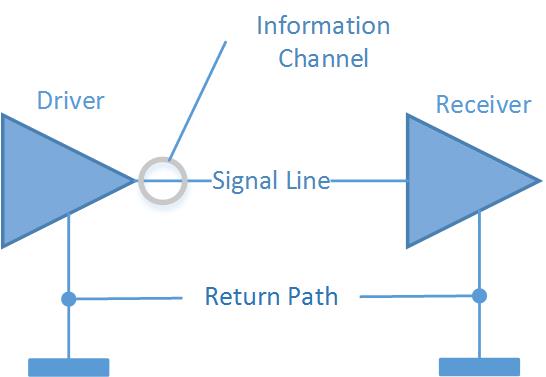

Single-Ended

Metoda SE znamená, že přenos je pro každý informační kanál prováděn právě přes jednu digitální signální linku, a signálová zem (tzv. ground return path) je společná pro všechny digitální linky. Systémy SE vyžadují pouze jednu linku na signál. Jedná se o nejrozšířenější druh přenosu digitálních signálů, uplatňující se zejména mezi jednotlivými bloky vlastního integrovaného obvodu, nebo skupiny integrovaných obvodů na desce plošných spojů.

Metoda SE znamená, že přenos je pro každý informační kanál prováděn právě přes jednu digitální signální linku, a signálová zem (tzv. ground return path) je společná pro všechny digitální linky. Systémy SE vyžadují pouze jednu linku na signál. Jedná se o nejrozšířenější druh přenosu digitálních signálů, uplatňující se zejména mezi jednotlivými bloky vlastního integrovaného obvodu, nebo skupiny integrovaných obvodů na desce plošných spojů.

Důležitou vlastností je tedy reagování vstupních logických obvodů na napětí vztažené vůči zemnímu potenciálu VEE/VSS/GND.

Výhodou je nízká cena a jednoduchost linek.

Naopak nevýhody jsou malá imunita vůči rušení při vyšších rychlostech nebo delších vedeních, zdroj rušení pro ostatní signálové linky a sdílená signálová zem, která obsahuje řadu vysokofrekvenčních složek – šum (VG – Ground Noise Voltage).

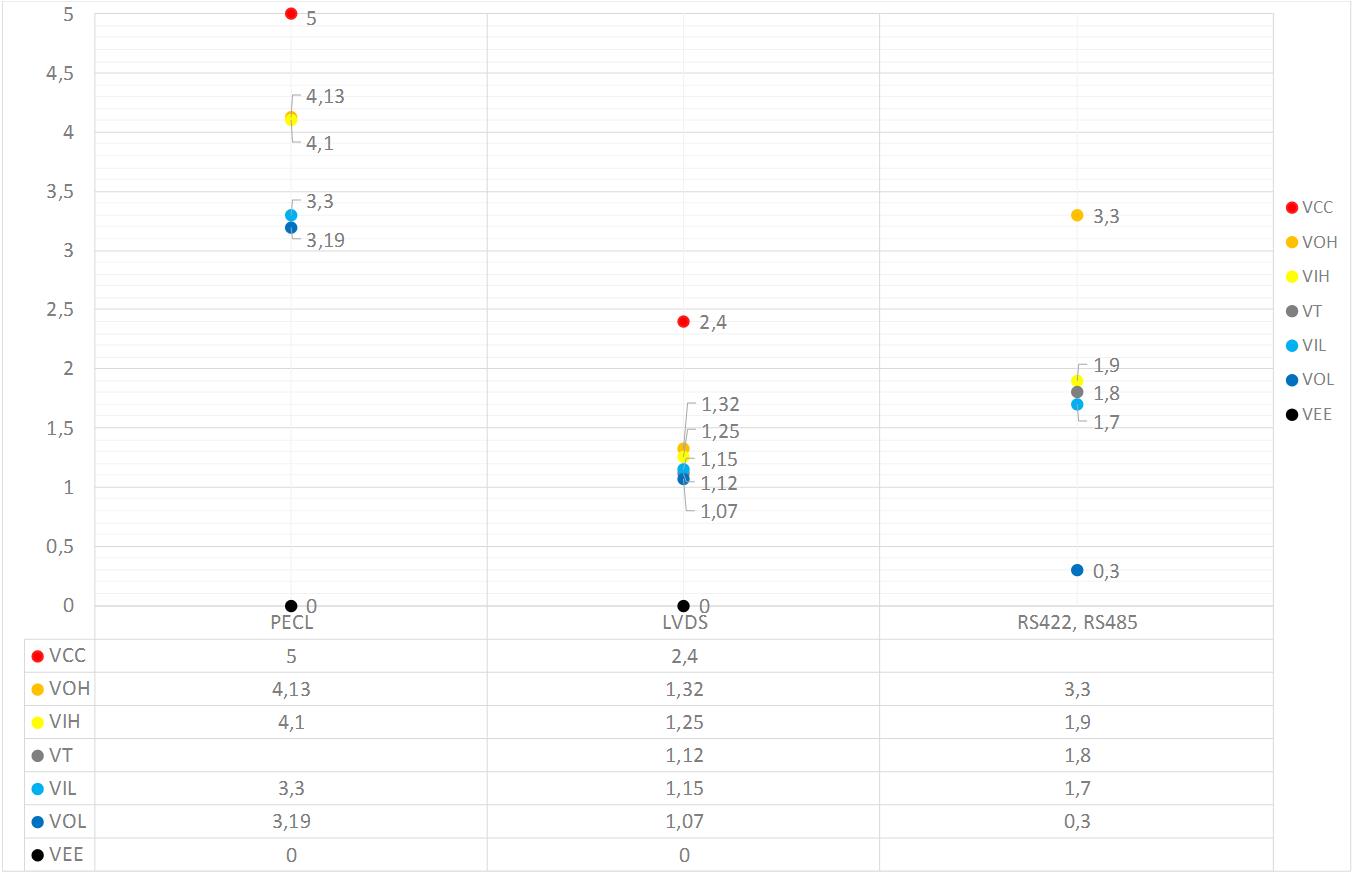

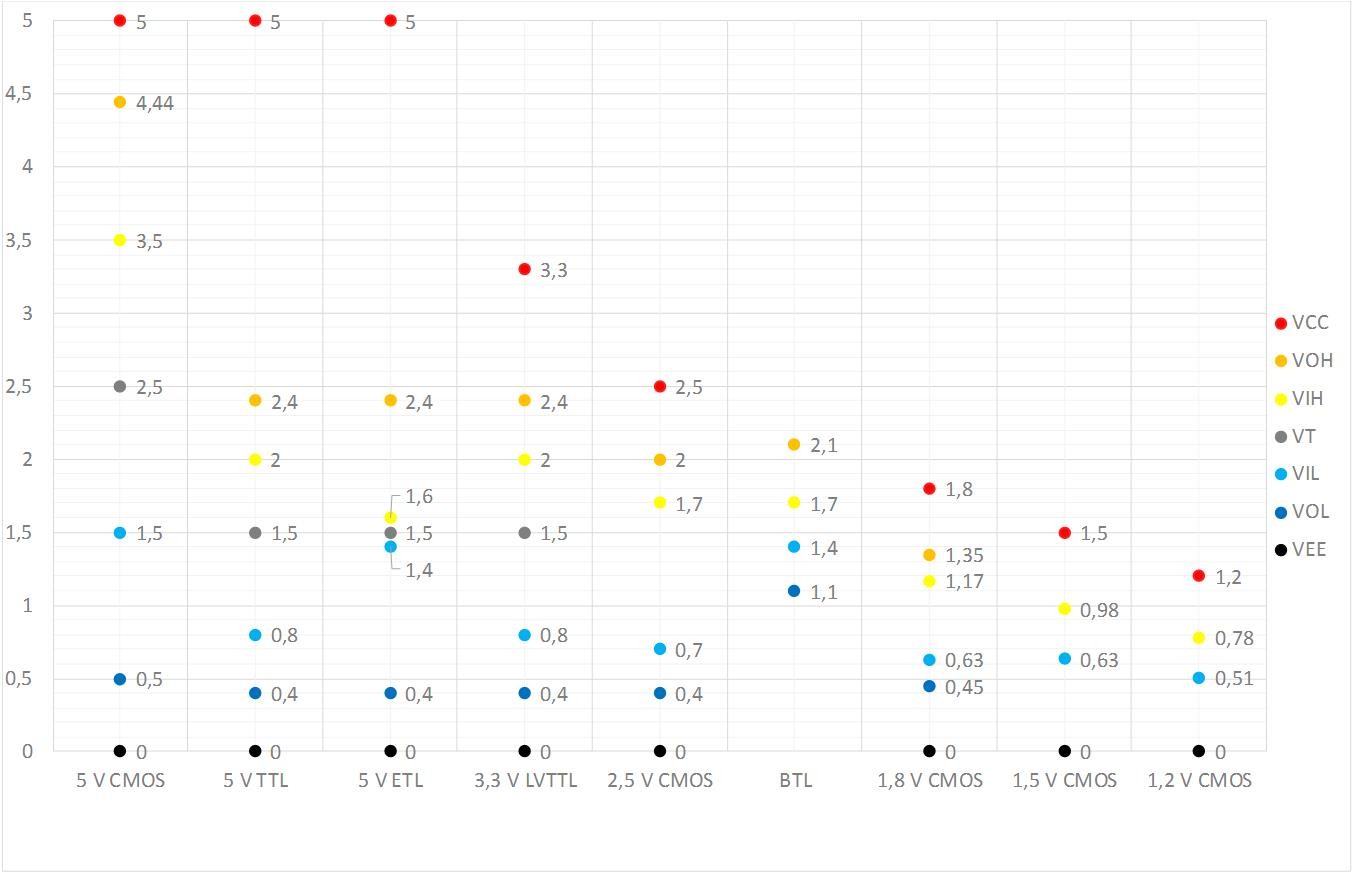

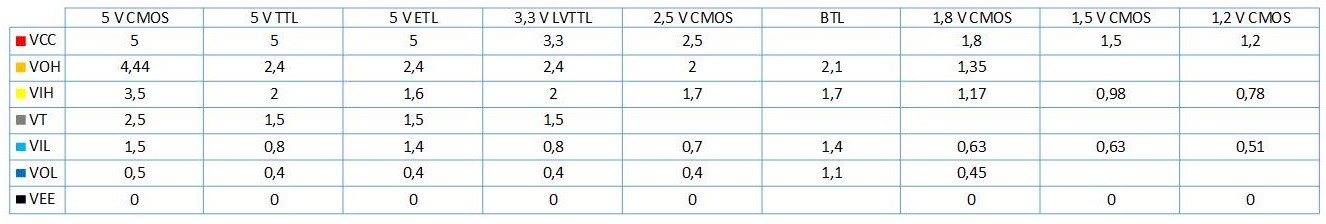

Na obrázku, a v tabulce, níže jsou uvedeny nejpoužívanější napěťové úrovně uplatňující se při přenosu digitálních signálů:

U signálů s napěťovými úrovněmi TTL pracujeme s absolutní hodnotou napětí. V případě CMOS jsou tyto hodnoty procentuální poměry odvíjející se od velikosti napájecího napětí VDD. Pro jednoduchost jsou již tyto poměry v tabulce přepočteny.

SE můžeme nalézt například u rozhraní: RS-232 (má vlastní napěťové úrovně ± 12 V; případně je k dispozici nekompatibilní verze TTL), I2C, SPI, PCI, VGA, SCSI, PATA, atp.

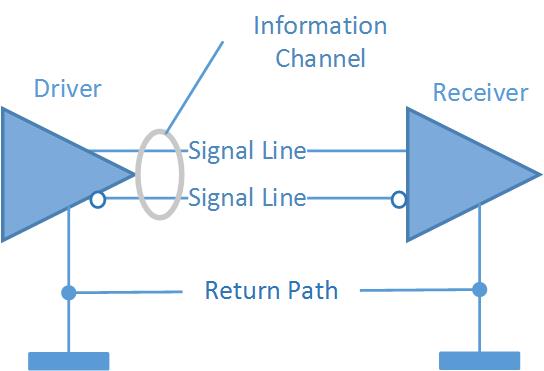

Diferenciální

Oproti metodě Single-Ended, metoda diferenciální využívá pro přenos informačního kanálu dvojici signálových digitálních linek.

Oproti metodě Single-Ended, metoda diferenciální využívá pro přenos informačního kanálu dvojici signálových digitálních linek.

Při generování digitálního signálu je využito komplementární dvojice výstupů. Diferenciální vstupní obvody následně vyhodnocují rozdíl napětí mezi dvojicí signálových linek, místo jeho vztahování vůči zemnímu potenciálu, jako v případě SE.

Mezi výhody patří vyšší imunita vůči okolnímu rušení a díky tomu i užší zónu rozhodovacích úrovní. Současně není do okolního prostředí vyzařováno tolik rušivé energie.

Nevýhodou je větší složitost a cena obvodů, jelikož každý informační kanál využívá právě dvojici signálních datových linek. Při diferenciálním přenosu digitálního signálu je možné dosahovat větších vzdáleností (jednotky km) nebo vyšších rychlostí přenosu (stovky Gbps).

Důležitým parametrem, který je nutné brát v úvahu při návrhu, je charakteristická impedance, která je pro každý typ napěťových úrovní jiná.

Na obrázku, a v tabulce, níže jsou uvedeny nejpoužívanější napěťové úrovně uplatňující se při přenosu digitálních signálů:

Na některé výstupy integrovaných obvodů pracujících v diferenciálním režimu (např. oscilátory a generátory hodinového signálu) lze bez problémů připojit SE vstup. V takovém případě zůstane komplementární výstup odpojen. Vždy je ale nutné dodržet napěťovou kompatibilitu pro logickou 1 a 0. Více informací o podpoře této možnosti u konkrétního integrovaného obvodu lze nalézt v příslušném datovém listu.

Na některé výstupy integrovaných obvodů pracujících v diferenciálním režimu (např. oscilátory a generátory hodinového signálu) lze bez problémů připojit SE vstup. V takovém případě zůstane komplementární výstup odpojen. Vždy je ale nutné dodržet napěťovou kompatibilitu pro logickou 1 a 0. Více informací o podpoře této možnosti u konkrétního integrovaného obvodu lze nalézt v příslušném datovém listu.

Diferenciální metodu přenosu používají např. rozhraní: USB, RS-422, RS-485, SATA/SAS, Infiniband, PCIe, ethernet (kroucená dvoulinka), FireWire, HDMI, atd.

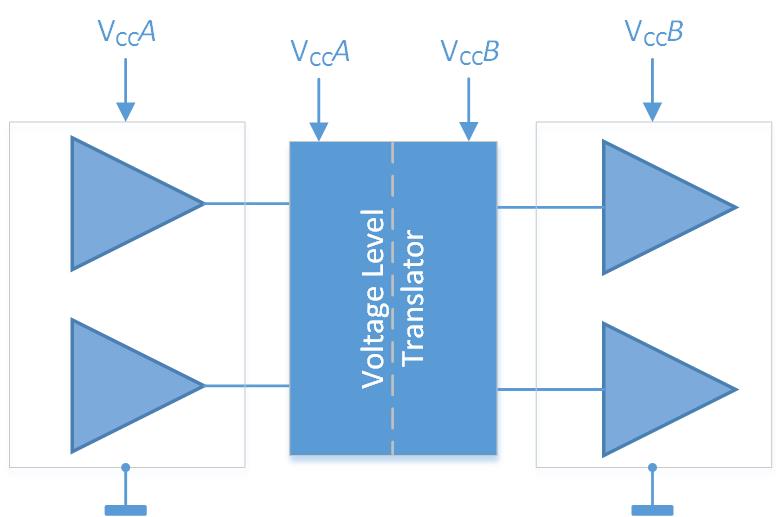

Převody napěťových úrovní

Vzhledem k množství používaných napěťových úrovní v digitální technice, je důležitá vzájemná propojitelnost jednotlivých čipů.

Aby byla zajištěna schopnost přepínat logické hodnoty 1 a 0, je potřeba splnit několik základních potřeb:

- VOH musí být větší než VIH

- VOL musí bít menší než VIL

- Maximální a minimální úrovně napětí musí být v toleranci vstupní logiky.

V případě, že tomu tak není, použijeme speciální integrované obvody, které provádí převody těchto napěťových úrovní.

V případě, že tomu tak není, použijeme speciální integrované obvody, které provádí převody těchto napěťových úrovní.

Použijeme-li ale takový integrovaný obvod, musí, kromě převodů správných napěťových úrovní, mít minimální vliv na převáděný digitální signál. To platí zejména pro rychlost, s jakou dokáže obvod pracovat, a zpoždění propagace signálu.

Pingback: Arch Linux on Orange Pi Zero | brichacek.net